Increasing Automation to Reduce Post-Silicon Characterization by Over 60%

- markvasat

- Aug 25, 2023

- 6 min read

Updated: Aug 28, 2023

*As Featured on NI.com

Original Authors: Vinodh J Rakesh, Cypress Semiconductor Technology India Pvt. Ltd.

Edited by Cyth Systems

The Challenge

Reducing the turnaround time for the bench characterization of diverse System-on-Chip (SoC) products designed and developed at different Cypress centers in Asia and America.

The Solution

Developing an ATE like characterization platform called CyMatrix using NI PXI Source Measure Units, PXI Matrix Switch Modules and FlexRIO modules with built-in support for up to 4X parallelism without sacrificing the flexibility or the signal integrity of a bench characterization environment.

Cypress Semiconductor Corporation (NASDAQ: CY) is a leader in advanced embedded system solutions for the world’s most innovative automotive, industrial, home automation, consumer electronic and medical product applications. Our Microcontroller and Connectivity Division (MCD) focuses on high-performance microcontroller units (MCUs), analog, wireless, and wired connectivity solutions. The portfolio includes Traveo™ automotive MCUs, PSoC® programmable MCUs, and general-purpose MCUs with ARM® Cortex®-M4/M3/M0+/R4 CPUs, analog PMIC Power Management ICs, CapSense® capacitive-sensing controllers, TrueTouch® touchscreen, Wi-Fi®, Bluetooth®, Bluetooth Low Energy and ZigBee® solutions. It also features a broad line of USB controllers, including solutions for the USB-C and USB Power Delivery (PD) standards. MCD generated revenue of about $1.4B in FY2017 while serving automotive customers like Continental, Denso, Visteon, Toyota, and BMW.

Time-to-Market Pressure Driving the Need for Efficient Silicon Characterization

Around 2011, driven by intense time-to-market pressure and customer requirements in the mobile touchscreen market, Cypress reduced the product development cycle time drastically by following a novel IP-based design approach. This approach decreased the time taken to tape out a chip and reduced the number of bugs we identified post silicon. Because of these factors, we saw a sudden spurt in the number of new products being launched. The design team was capable of taping out more products, but the characterization team wasn’t ready to characterize all the products on time.

The characterization team at Cypress is responsible for guaranteeing the datasheet specifications across PVT before releasing the product for volume manufacturing. On an average, each product has about 400 datasheet specifications. To guarantee fitness for volume production, we much measure each of these 400 specifications on anywhere between 6 and 50 DUTs. To meet the customer schedule requirements, we must complete the entire characterization of the product in four to eight weeks from silicon availability, depending on the complexity of the product. If we do not complete the characterization of the product within four to eight weeks, we risk delays in product launches, potentially leading to loss of customers and millions of dollars of business. Driven by the business requirement to be first and relevant in the market space, we knew we had to increase the efficiency of bench characterization.

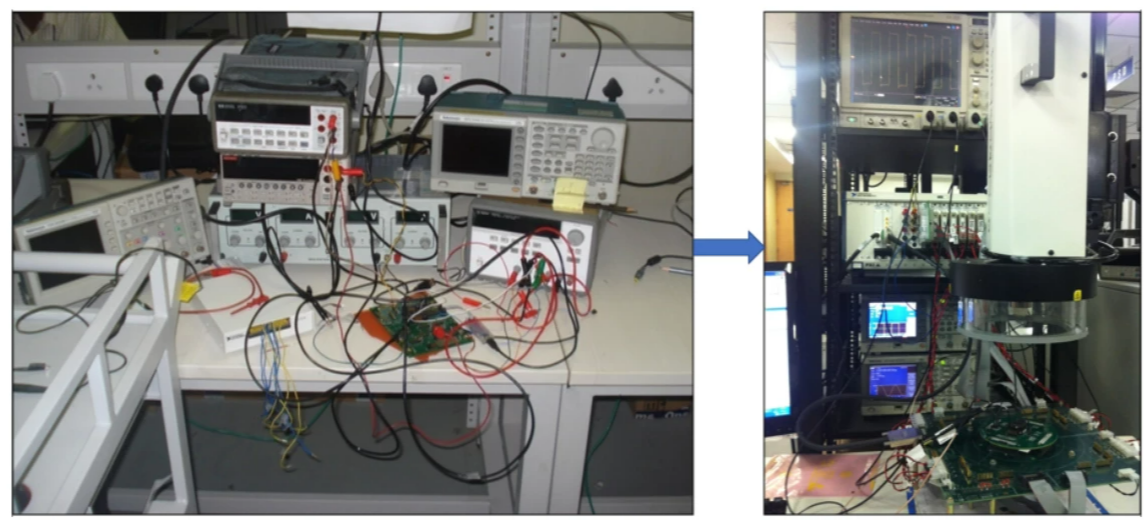

Left: Transition From a Bench Setup With Six Discrete Box Instruments to the Standardized CyMatrix Setup With 34 Instruments, Right: Architecture of the LabVIEW Characterization Process

Boosting Characterization Efficiency by Increasing Parallelism, Automation, and Standardization of the Bench Characterization Setup

The characterization team explored three ways to achieve higher efficiency: (1) increased parallelism, (2) increased automation and (3) increased code reuse/standardization. We had to scale the traditional bench characterization setups, which were limited to one DUT at a time with 50 percent automation, to achieve truly parallel characterization that gives every DUT its own dedicated instruments or at least enough instruments to allow for time-division multiplexing with > 90% automation.

To characterize a typical PSoC DUT, we have to do current/voltage/timing measurements on 64 signal pins and 4 power pins. Therefore, we need 68 source measure units (SMUs)to perform all applicable tests. Factoring in a 4X parallelism, we need a characterization setup including 272 SMUs. Conventional production floor automated test equipment (ATEs) offer channel counts of this order, but they often fall short on the accuracy required for bench characterization. Besides, replicating an ATE architecture for bench is prohibitively expensive. Although a DUT has 68 pins across which the measurements must be made, the measurements need not be done simultaneously across all these pins. A careful study of all the test cases showed that, we need access to, at most, 4 signal pins and 4 power pins simultaneously. Hence, we built the entire characterization setup with just 32 high-precision SMUs, which were multiplexed across all 272 pins of the 4 DUTs being tested using a switch-matrix arrangement. The test setup includes two NI 2532 PXI Matrix Switch modules, which are 512-crosspoint switch matrices. The LabVIEW-based characterization program makes the requisite connections at run time between the DUT pins and the SMU channels based on the test requirements. The architectural diagram is shown in Figure 1. Despite the use of switch matrices, we still need 32 SMUs for the complete bench characterization setup. We ruled out traditional benchtop SMUs because they occupied too much space and involved additional cabling efforts. Instead, we chose to use NI’s PXI 4-channel SMUs, and with eight of these PXI modules, we met all the setup requirements.

Some products, such as the Traveo II Automotive MCUs, could also function as multiple protocol masters—DDR HSSPI, Hyperbus, SPI and SDHC. Hence, the characterization process for these DUT variants involves source synchronous measurements. In source synchronous measurements, the DUT provides the clock and the external instrument drives the data with respect to this input clock. Measurements also included shmoo’ing the data driven by the instrument with respect to the input clock at ~100 ps resolution while being protocol aware. Conventional pattern generators, high-speed digital I/O modules, and, in some cases, ATEs do not have good timing responses to external discontinuous clocks. The timing characterization of protocol masters is best implemented with actual protocol-aware slaves that can respond synchronously to the input clock. However, these slaves do not have the capability to shmoo the data with respect to the clock. Also, using slave devices often requires the use of external discrete components such as level shifters to ensure voltage compatibility between the master and the slaves, the programmable delay chains to shmoo the delay, and so on. Such setups including multiple slave devices and associated external components are complex and prone to system-level issues. To circumvent this problem of using actual slave devices, we turned to programmable NI PXI FlexRIO product family with programmable FPGAs to emulate the slave functionality. The FlexRIO devices also allowed us to implement programmable delays with ~40 ps resolution for fine delays and ~120 ps resolution for coarse delays. The front-end FlexRIO adapter module fulfilled the functionality of the level shifter between the DUT and the emulated slave. An NI Alliance Partner, Soliton Technologies Pvt. Ltd., helped us implement the slave functionality and programmable delays on the FPGA.

The transition from a single-site characterization setup to a multisite parallel characterization setup offered many benefits, so our engineering teams in Bangalore, Seattle, and Colorado immediately adopted this multisite platform. Before that, each center maintained setups with different instrumentation and had its own repository of code that was built and maintained only within these individual sites. The earlier approach limited code reuse and, at times, made replicating issues across sites difficult because of the lack of standardization in automation programs, characterization boards, and the instrumentation and interconnects. Standardization was immediately identified as the way forward, but it also presented some business constraints, like reusing existing instrumentation investments. To address this, we developed a framework based on LabVIEW object-oriented programming (LabVIEW OOP) concepts that provides an abstraction layer above the individual device driver on which we built the entire characterization automation program. This allowed engineers at different sites to seamlessly switch between instruments, such as SMUs, digital multimeters(DMMs), and arbitrary waveform generators(AWGs), from different vendors by simply editing a single entry on an Excel spreadsheet.

Translating Higher Characterization Efficiency into Organizational Benefits

The 4X parallelism has decreased characterization times, which has allowed us to identify and fix bugs more rapidly. The newer characterization setup has directly reduced our characterization time by over 60 percent. The characterization routine for medium-complexity products takes less than 4 weeks now as compared to 10 weeks earlier. We have also reduced the characterization time for highly complex products from 20 or more weeks to under 8 weeks.

Our characterization team’s head-count has not changed much from 2011. However, the same team can now characterize more than five products in a calendar year instead of the one or two, prior to automation of the setup. Standardization and code reuse have helped us reduce the time we need to prepare for a new silicon, avoid bugs, and improve the overall reliability of the characterization setup. Though engineers and teams from multiple sites sitting in different time zones contribute to the overall characterization efforts of a product, we have seen instances when bugs reported from one site were easily replicated at the other sites by the next day. This is a true testament to how standardization has helped increase our engineers’ productivity, as they spend more time on troubleshooting the reported bug instead of on reproducing bugs.

Original Authors:

Vinodh J Rakesh, Cypress Semiconductor Technology India Pvt. Ltd.

Edited by Cyth Systems

Comments